«Мультиклет»: завершены внутренние тесты первой партии мультиклеточных процессоров

Компания «Мультиклет» объявляет о завершении внутренних тестов первой опытно-промышленной партии мультиклеточных процессоров, выпущенной в июне.

Приводятся следующие параметры процессора:

кристалл с топологической нормой 180нм размером 10х10 мм в корпусе QFP-208, что обусловлено периферией: 2 интерфейса SPI с селектором “ведомых” устройств (в режиме “ведущий”), 4 универсальных асинхронных приёмопередатчика UART c FIFO на прием/передачу, 2 интерфейса I2C (один “master” и один “slave”), интерфейс I2S, Ethernet контроллер 10/100Мб/с, USB 1.1 FS (device) контроллер с последовательным внешним интерфейсом для подключения приемо-передатчика, часы реального времени с календарем, 7 таймеров общего назначения, 4 порта ввода-вывода, общее количество вводов-выводов – 104, 4-х канальный контроллер ШИМ, сторожевой таймер.

Выбор топологической нормы 180 нм обусловлен стоимостью начальной разработки и апробирования, а так же планируемой областью применения микропроцессора.

Подробная информация о мультиклеточной архитектуре, на основе которой создан микропроцессор MCp0411100101 находится на сайте компании в разделе поддержка, общетехническая информация. В тексте документа «Концепция мультиклеточного процессора» содержится подробная информация об описании и принципах построения процессора, а так же о его архитектурных особенностях.

«В ходе испытаний разработчиками нашей компании подтверждены ранее заявленные по микропроцессору характеристики, процессор и периферия работают штатно, - отметил генеральный директор ОАО «Мультиклет» Борис Зырянов. - Важно, что полученные в ходе тестов цифры, говорят о широких потенциальных возможностях мультиклеточной архитектуры».

Кстати, а вы знали, что на «Сделано у нас» статьи публикуют посетители, такие же как и вы? И никакой премодерации, согласований и разрешений! Любой может добавить новость. А лучшие попадут в наш Телеграм @sdelanounas_ru. Подробнее о том как работает наш сайт здесь👈

Другие публикации по теме

- В ТПУ (член Национальной ассоциации участников рынка робототехники) пр... тепла перестают справляться, что требует поиска более эффективных решений.

-

Студент РТУ МИРЭА Макар Климов представил мотор нового бироторного двигател...бщества изобретателей и рационализаторов III Конгресса молодых учёных.

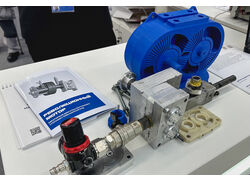

Студент МИРЭА представил мотор нового бироторного двигателя внутреннего сгорания с повышенным к.п.д.

Студент МИРЭА представил мотор нового бироторного двигателя внутреннего сгорания с повышенным к.п.д.

- Холдинг «СОЮЗСНАБ», крупнейший производитель пищевых ингредиент... 1000 тонн ароматических и вкусоароматических соединений в месяц.

Поделись позитивом в своих соцсетях

Комментарии 0